- userLoginStatus

Digital Integrated CIrcuit Design

Synthetic program:Introductory concepts and background

- A historical perspective: from vacuum tube to transistor and IC era Issues in digital integrated circuit design

- Implementation strategies for Digital ICs: Custom design and standard-cell based design

- Quality metrics of a digital circuit (cost of an integrated circuit, functionality and reliability, static and dynamic performance, power and energy consumption).

The devices:

- MOSFET transistor as switch

- Static and dynamic behavior

- Velocity saturation and unified model

- Mismatch and process variations

- Technology scaling

The wire:

- Interconnect parameters (capacitance, resistance and inductance)

- Electrical wire model (ideal wire, lumped model, lumped RC model, distributed rc line, P and T model)

- Elmore theorem

- Effects of scaling of wires and impact on the overall performances.

The CMOS inverter:

- The static CMOS inverter (switching threshold, noise margins, robustness revisited);

- Dynamic behavior (computing the capacitances, propagation delay)

- Power consumption (dynamic, cross-conduction, leakage)

- Power- and energy-delay product

- Inverter chain and optimum number of inverters in a chain with a capacitive load

- Technology scaling and its impact on the digital circuit metrics.

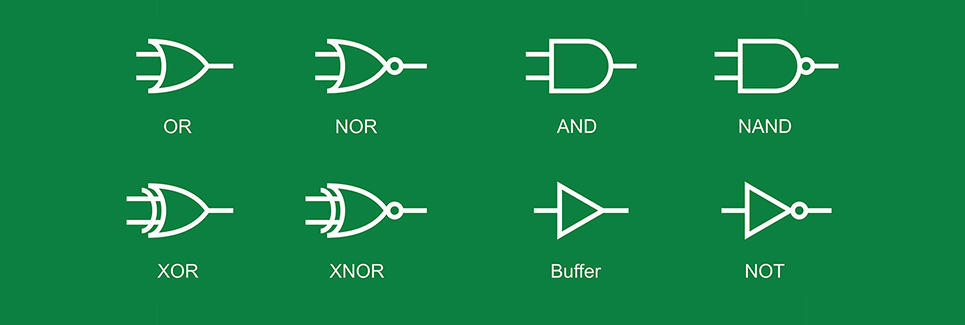

Combinational logic gates:

- Fully-complementary CMOS logic

- Sutherland theory on the dimension of FC-CMOS gate chain

- Ratioed logic, i.e., pseudo-NMOS logic and differential cascode voltage switch logic (DCVSL)

- Pass-transistor logics, i.e., LEAP (LEAn Integration with pass-transistors), Swing Restored Pass Transistor Logic (SRL), Complementary Pass-transistor Logic (CPL)

- Transmission gate

- Dynamic logic (basic principles, speed and power dissipation of dynamic logic, signal integrity issues in dynamic logic, cascading dynamic gates, domino gates)

- Domino logic and relative issues

- Differential domino logic and NORA

Sequential logic circuits:

- Latches and flip-flops as basic sequential element

- Timing metrics for sequential circuits

- Static latches and flip-flops (the bistability principle, multiplexer-based latches, master-slave edge-triggered flip-flops, Low-Voltage Static Latch, Static SR flip-flop with pure force writing)

- Dynamic latches and flip-flops, i.e., basic topology, C2MOS latch, True Single-Phase Clocked (TCSP) flip-flops

- Pulsed flip-flops

- Pipelining as approach to optimizing sequential circuits

- Finite state-machines (FSMs), counters asynchronous and synchronous

- Timing classification of digital systems (synchronous, mesochronous, plesiochronous, asynchronous)

- Synchronous design, self-timed circuit design, synchronizer and arbiters

Arithmetic circuits:

- Datapath in digital signal processor

- The adder (half-adder and full-adder)

- Circuit implementation of single-bit adder (static implementation, mirror adder, CPL,

- Multi-bit adder (ripple carry, carry-skip, linear carry-select, root-square carry-select, carry-lookahead)

- Multipliers (array and carry-save multiplier) 2’complement form of signed numbers

- Digital comparators, subtractors, equality circuits.

Semiconductor memories:

- Memory classification

- Memory architectures and building blocks

- Read-only memories (ROM), NOR and OR ROM architectures

- Nonvolatile read-write memories (EPROM, EEPROM, flash)

- Static RAM with resistive load, 6T static RAM

- Dynamic RAM (1T, 3T), open and folded bit line architecture

- Memory peripheral circuitry (address decoders, sense amplifiers, voltage references, drivers/buffers).

Lecture Notes

Complete course:

| Type | File name | Year |

|---|---|---|

| Handwritten notes | Complete course notes | 2019/2020 |

Divided by topic:

| Type | File name | Year |

|---|---|---|

| File not available... | ||

Other:

| Type | File name | Year |

|---|---|---|

| File not available... | ||

Exercises

Complete course:

| Type | File name | Year |

|---|---|---|

| Handwritten notes | Exercises of the course | 2019/2020 |

Divided by topic:

| Type | File name | Year |

|---|---|---|

| File not available... | ||

Other:

| Type | File name | Year |

|---|---|---|

| File not available... | ||

Exams

First partial exam:

| Type | Date | |

|---|---|---|

| File not available... | ||

Second partial exam:

| Type | Date | |

|---|---|---|

| File not available... | ||

Full exam:

| Type | Date | |

|---|---|---|

| File not available... | ||

Oral exam:

| Type | Date | |

|---|---|---|

| File not available... | ||

Multiple choice test:

| Type | Date | |

|---|---|---|

| File not available... | ||

Other:

| File name | ||

|---|---|---|

| File not available... | ||

Other

Laboratory:

| File name | Year | |

|---|---|---|

| File not available... | ||

Projects:

| File name | Year | |

|---|---|---|

| File not available... | ||

Presentations:

| File name | Year | |

|---|---|---|

| File not available... | ||

Collections of notes, exercises or exams:

| File name | Year | |

|---|---|---|

| File not available... | ||

Tables:

| File name | Year | |

|---|---|---|

| File not available... | ||

Etc:

| File name | Year | |

|---|---|---|

| File not available... | ||

Live

Quick daily notes, exercises and audio recordings. Files will be approved on priority but deleted after 365 days. 2 points will be assigned by default.

Quick contents:

| File name | Date | |

|---|---|---|

| File not available... | ||